According to Guru3D.com, AMD has officially confirmed that its upcoming Medusa and Venice processors will utilize the Zen 6 architecture during the 2025 OCP Global Summit. The revelation came directly from AMD Fellow Raj Kapoor and AMI’s Boot Firmware VP, confirming months of industry speculation. Venice represents AMD’s next-generation EPYC server processors built on TSMC’s 2nm process, scheduled for 2026 release alongside AMD’s openSIL open-source firmware framework. For consumers, the Zen 6-based Ryzen series carries the Medusa codename, with Medusa Ridge for desktops maintaining AM5 socket compatibility and Medusa Point for laptops, both targeting early 2027 availability with openSIL support rolling out in the first half of that year. This confirmation sets the stage for AMD’s most significant architectural transition in years.

The Zen 6 Architectural Leap: Beyond Process Shrink

While the move to TSMC’s 2nm process represents a significant manufacturing advancement, the real story lies in what AMD can achieve architecturally with Zen 6. The transition from Zen 5 to Zen 6 likely represents AMD’s most substantial microarchitectural overhaul since the original Zen debut in 2017. We’re looking at potential innovations including advanced chiplets with 3D stacking, possibly incorporating compute dies, I/O dies, and cache layers in sophisticated three-dimensional arrangements. The architectural improvements will likely focus on AI acceleration, with dedicated matrix math units becoming standard across both server and consumer segments. This isn’t merely a process shrink – it’s a fundamental rethinking of how AMD approaches compute density and specialized acceleration.

OpenSIL: The Silent Revolution in Firmware

The openSIL framework represents one of AMD’s most strategic long-term plays, potentially reshaping enterprise computing infrastructure. Unlike traditional BIOS/UEFI implementations that rely heavily on proprietary code, openSIL provides a transparent, open-source silicon initialization layer that could dramatically reduce firmware complexity and improve security auditing. For enterprise customers, this means faster vulnerability patching, reduced vendor lock-in, and greater customization capabilities. The framework’s deployment timeline – arriving with Venice servers in early 2026 before reaching consumer platforms in 2027 – indicates AMD’s enterprise-first strategy, where mission-critical reliability requirements drive initial implementation before trickling down to consumer markets.

AM5 Socket Longevity: Strategic Brilliance or Technical Limitation?

AMD’s decision to maintain AM5 socket compatibility for Medusa Ridge desktop processors represents both a consumer-friendly move and a calculated technical decision. While this ensures motherboard reuse and reduces platform costs for upgraders, it also imposes significant engineering constraints. The socket’s power delivery specifications and pin configurations must accommodate not just current Zen 4 and upcoming Zen 5 processors, but also the more demanding Zen 6 architecture two generations later. This suggests AMD’s confidence in AM5’s fundamental design, but also raises questions about whether socket limitations might constrain Zen 6’s performance potential. The balancing act between backward compatibility and forward innovation will define AMD’s consumer strategy through 2027.

Server Market Implications: Venice’s 2nm Advantage

Venice EPYC processors arriving on TSMC’s 2nm process in 2026 position AMD to maintain its server market momentum against Intel’s upcoming offerings. The 2nm node represents approximately a 15-20% performance improvement at equivalent power, or 30-35% power reduction at matched performance compared to current 3nm technology. For data center operators, this translates to meaningful reductions in operational costs and power density improvements. More importantly, Venice’s timing aligns perfectly with the maturation of AI inference workloads in enterprise environments, suggesting AMD is optimizing its server roadmap specifically for the next phase of AI adoption beyond current training-intensive applications.

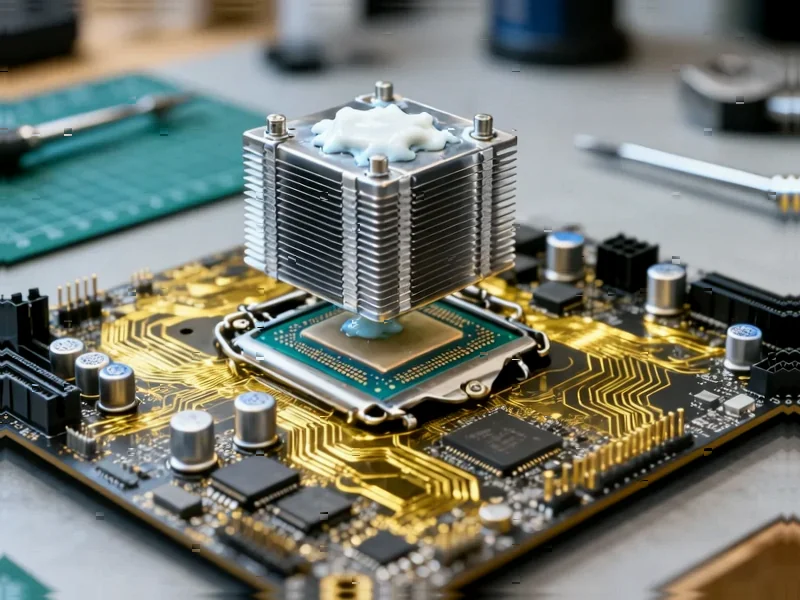

The Implementation Challenge: From Blueprint to Silicon

The roadmap from current Zen 4 to Zen 6 by 2026-2027 represents an aggressive cadence that presents significant engineering challenges. Each architectural generation requires not just new core designs but also sophisticated packaging technologies, memory controller enhancements, and I/O subsystem improvements. The transition to 2nm manufacturing brings its own complexities, including yield optimization and thermal management considerations. Additionally, coordinating the openSIL framework development alongside silicon design adds another layer of complexity to an already challenging timeline. AMD’s ability to execute on this ambitious roadmap will depend heavily on maintaining its engineering talent and managing the increasing complexity of modern processor design.